- #Review of smartpls 3 methodology and software full#

- #Review of smartpls 3 methodology and software software#

- #Review of smartpls 3 methodology and software simulator#

Since pre-designed inductorsĪvailable from the vendor were not used here, custom inductor models were used toĬorrectly model spiral inductors. Virtuoso Schematic Editor by instantiating components that have been SPICE modelledĪnd provided by AMS and connecting them by wires. Was developed in parallel or otherwise, schematics of each test circuit was drawn in After being conceptually designed, whether using a design routine that Modelling and simulation were done in Virtuoso Schematic Editor, ADE, Spectre and

Layout generation, design checks and layout versusĮlectromagnetic (EM) simulation of spiral inductors

#Review of smartpls 3 methodology and software simulator#

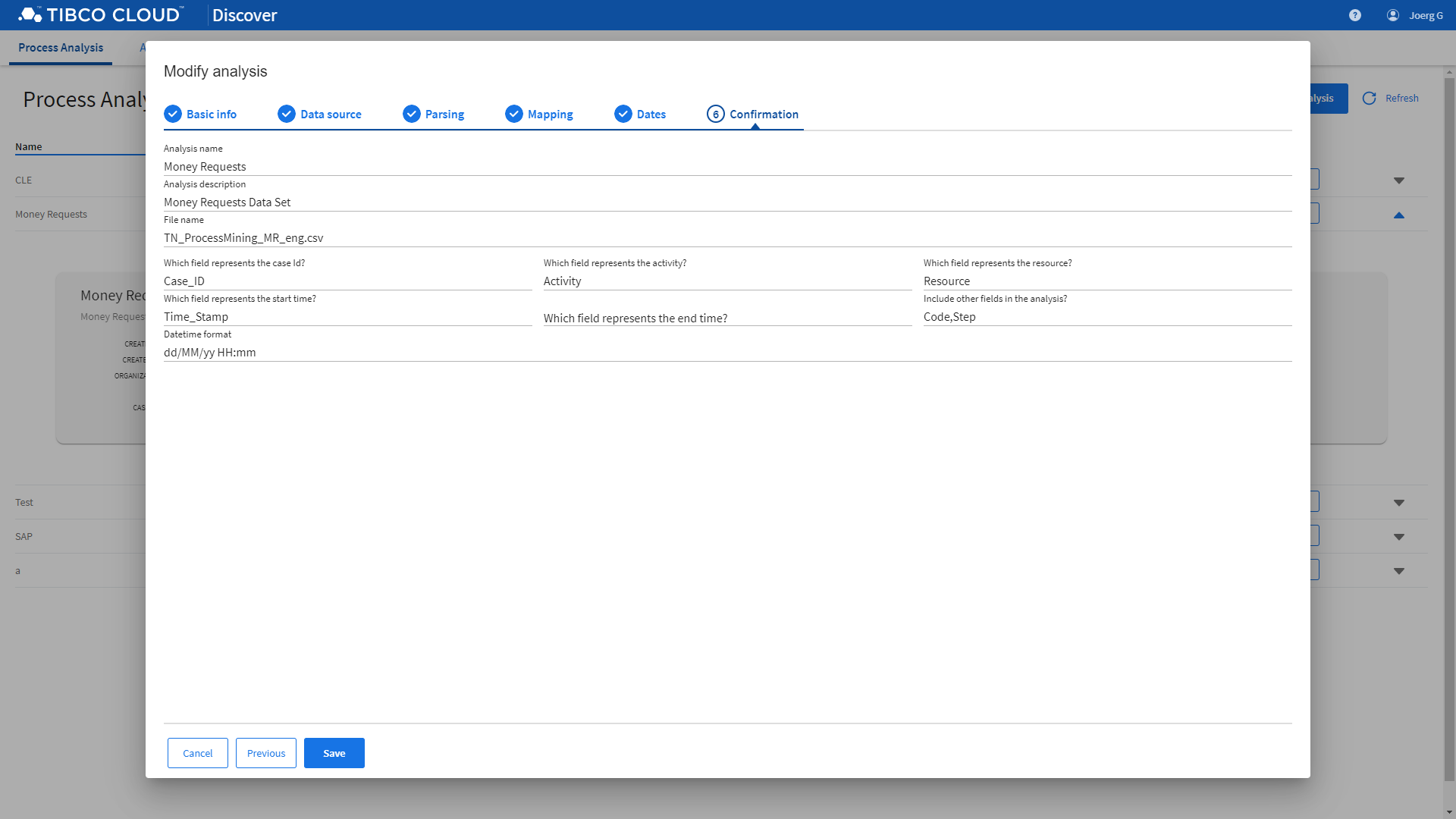

With Spectre and SpectreRF Circuit Simulator Tools of Cadence Virtuoso package and their functionality. Several tools available in this package were used,Īnd their names and functionality are given in Table 3.1. Modelling and simulation of various PA circuits was performed in Cadence Virtuoso This version did not have a graphical user interface (GUI) front-end for the algorithms, theĮase of use of MATLAB programming language simplified debugging. The same package was used to design the first version of the PA design routine. Number of mathematical functions, and it can be used to speed up tedious hand This package is a programming language that supports a great

#Review of smartpls 3 methodology and software full#

Signed with IBM for full process parameters please refer to if available.ĬONCEPTUAL DESIGN AND ALGORITHM DEVELOPMENTĬomplete conceptual design and mathematical modelling was done with the aid of

Polysilicon widths and spacing than for the AMS process. Process are similar to those of the AMS process except for differences, inter alia, inĪvailable capacitors and inductors, and the fact that design rules allow for smaller wire and The technology node in which circuits needed toīe completed was the 7WL 180 nm process from IBM. Sponsored by Metal Oxide Semiconductor Implementation Service (MOSIS) as a part

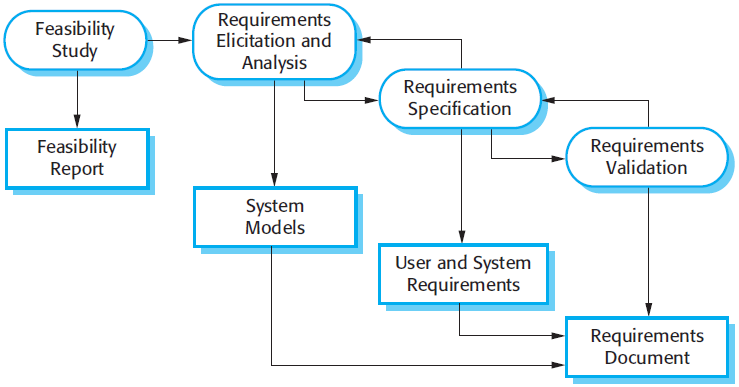

Measurements were essential for the works of this thesis. Signed between the author (via University of Pretoria) and AMS. Parameters cannot be disclosed in this thesis due to the non-disclosure agreement (NDA) Libraries of standard metal-3 (3M) and thick-metal (TM) spiral inductors. It is a SiGe BiCMOS process with NPN HBTs, PIP and MIM capacitors and several The main process chosen for this thesis is S35 0.35 µm SiGe BiCMOS process from AMS IC process parameters in order to work correctly. Spiral inductor part of the PA design routine must be able to interpret the Physical layout of the PA and inductor systems are drawn in conformity with theĭesign rules specific to a particular IC process.Ĭorrect modelling of spiral inductors is process dependent, as described in The IC process is significant because of the following reasons:Īll simulations are performed using the SPICE models particular to the IC process. Research methodology followed in this thesis. Research methodology followed in this thesis is graphically represented by the flowĭepartment of Electrical, Electronic and Computer Engineeringįigure 3.1. Of the fabricated IC presents a good way to get an insight into the quality of operation of Parasitics, which is particularly important for the RF circuits. This includes investigation of the influence of The IC is to be used to characterise effects Following successful simulations, a layout, essentially aīlueprint for the IC prototype, was developed. In parallel with research and development of the set of algorithms for PA automation in Revolved around designing PAs and spiral inductors, which could be critically evaluated,ĭesign and simulation of various PA stages in CAD tools described later in Section 3.5 ran

#Review of smartpls 3 methodology and software software#

Software package for algorithm development.ĭue to the fact that the concepts applied in developing a method for rapid PA design had toīe transformed into circuits that can be simulated and tested, a major part of this research Packages used in the course of the research, such as the software package for conceptualĭesign, CAD packages for simulation and layout, measurement equipment, as well as the A part of the chapter deals with various software Key concepts and prototype the test chip. It starts with the flow of the research processĪnd continues with the description in some detail of the technologies used to simulate the This chapterĭescribes methodology used for this research. Chapter 2 provided a review of literature related to the topic of the thesis.

0 kommentar(er)

0 kommentar(er)